AI

AIApplication Specific Integrated Circuit (ASIC) Floorplan Automation - Part II

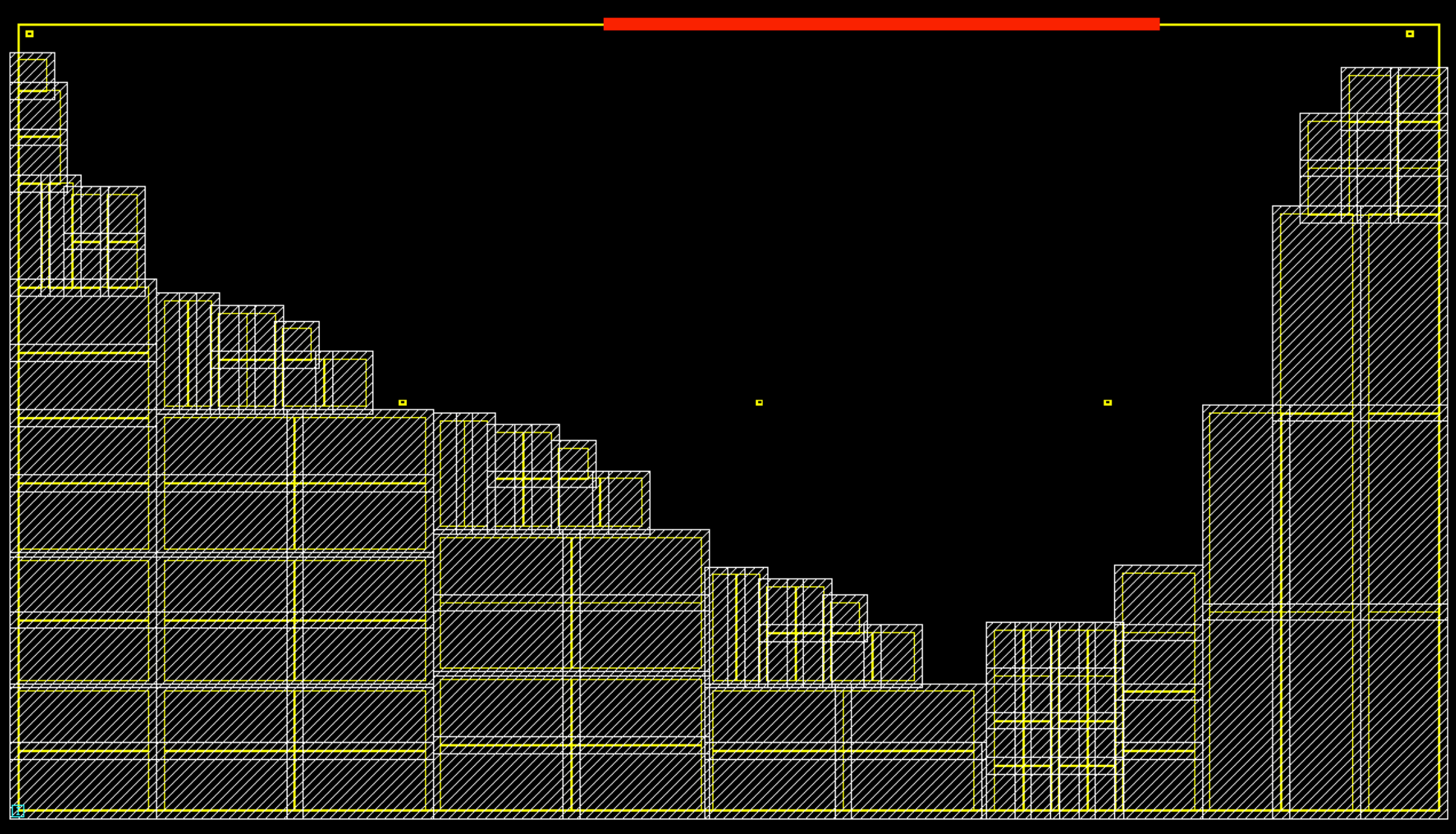

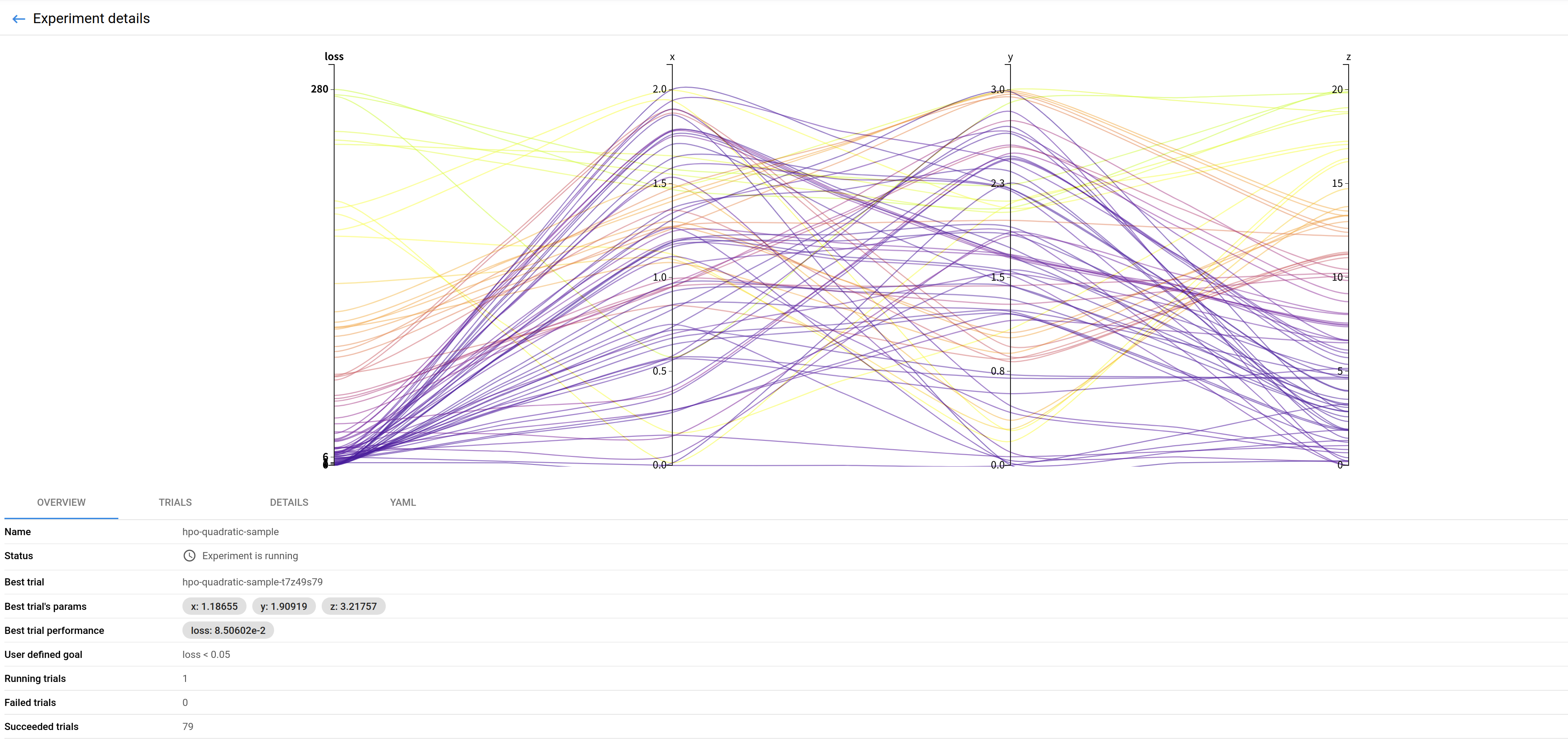

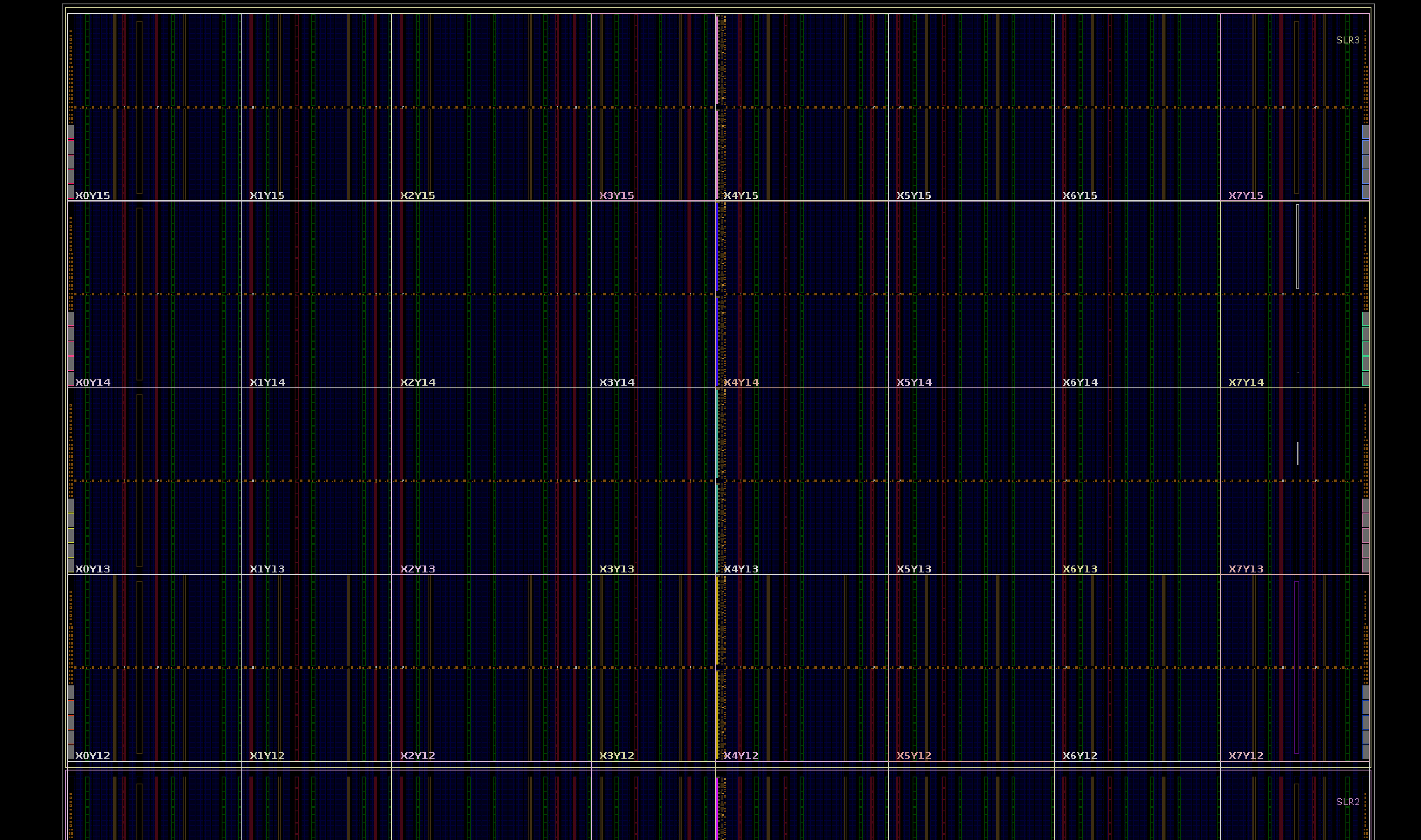

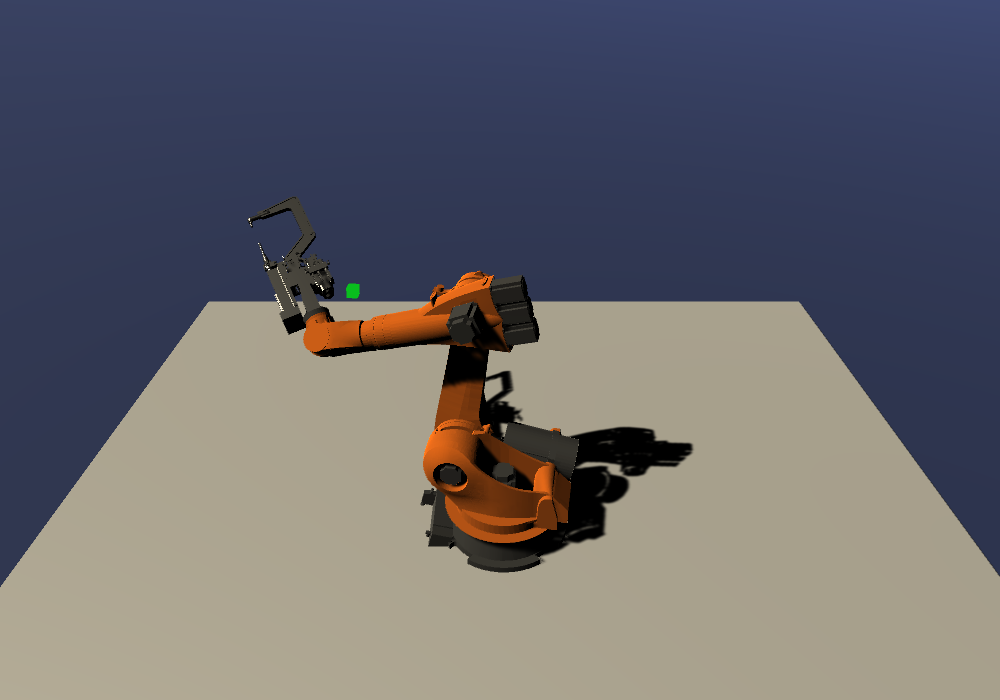

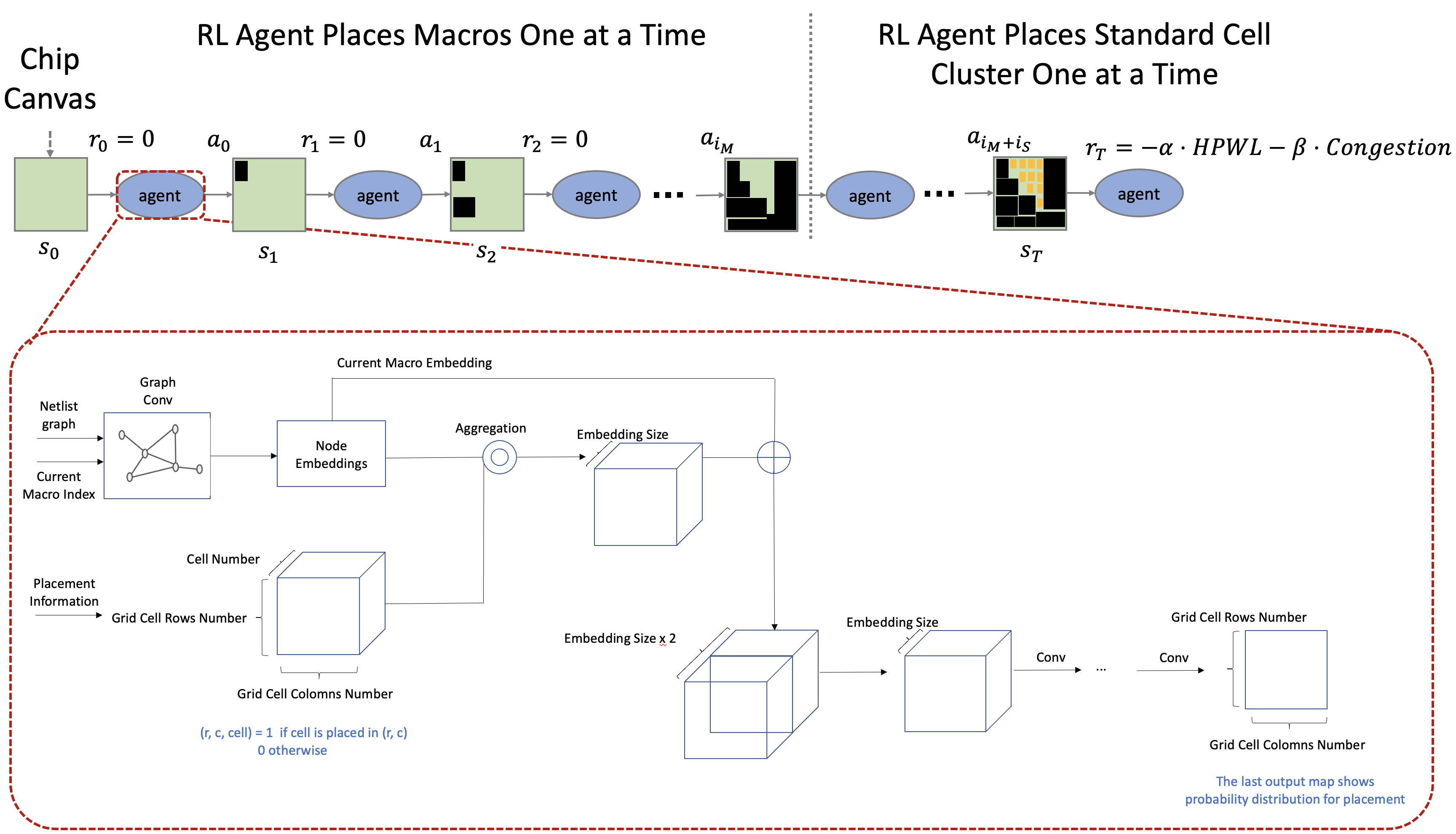

본 글은 ASIC 반도체 설계 과정 중 플로어플랜 단계의 배치 최적화 문제를 강화학습으로 해결하는 방법을 다룹니다. 특히, Naver Deview 21 발표 내용을 기반으로 하며, 이전 글에서 설명된 과정들을 거쳐 강화학습 에이전트가 칩 배치 문제를 학습하는 과정을 시각 자료와 함께 보여줍니다. 애니메이션은 약 1500번의 학습 반복 후 매크로(대형 녹색 사각형)와 표준 셀 클러스터(소형 파란색 사각형)의 배치가 안정화되는 과정을 나타냅니다. 학습을 통해 에이전트는 매크로를 칩 바깥쪽에, 표준 셀 클러스터를 안쪽에 배치하는 방법을 학습했음을 알 수 있습니다. 이는 칩 설계의 핵심 단계인 플로어플랜 최적화에 강화학습을 적용하여 효율성을 높일 수 있음을 시사합니다.