Chip Placement with Deep Reinforcement Learning

Chip PlacementDeep Reinforcement Learning반도체 설계조합 최적화Google논문 리뷰

AI 요약

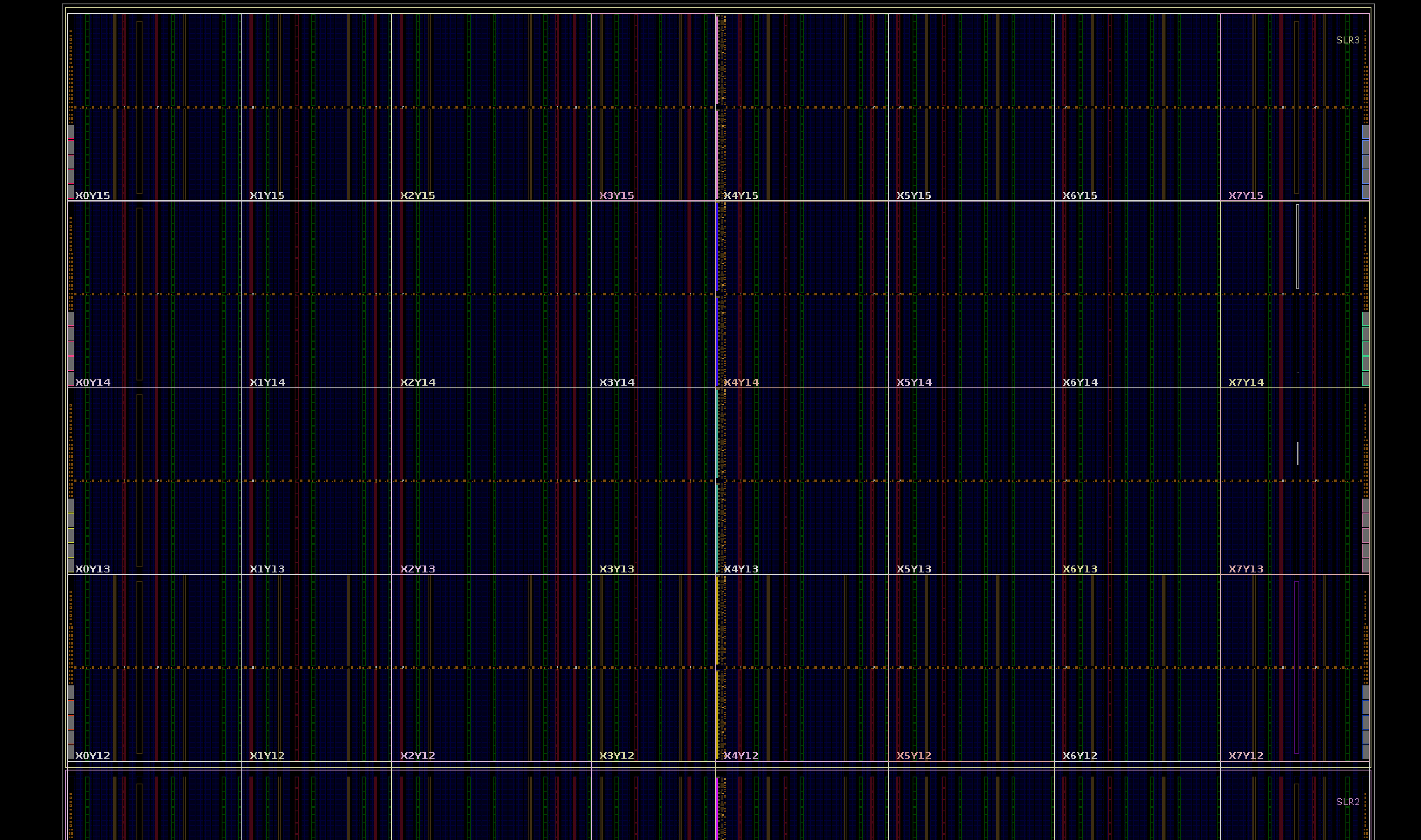

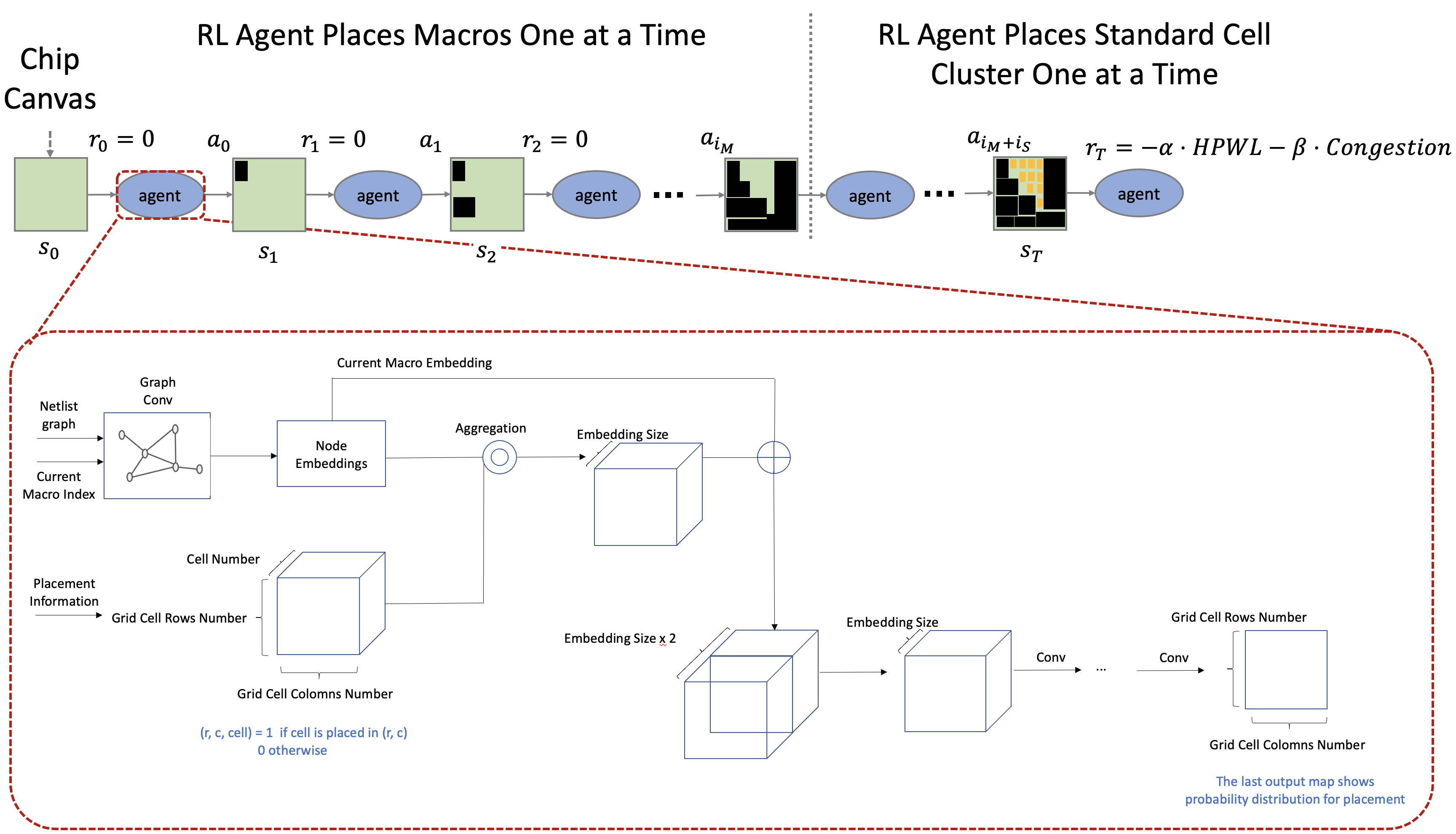

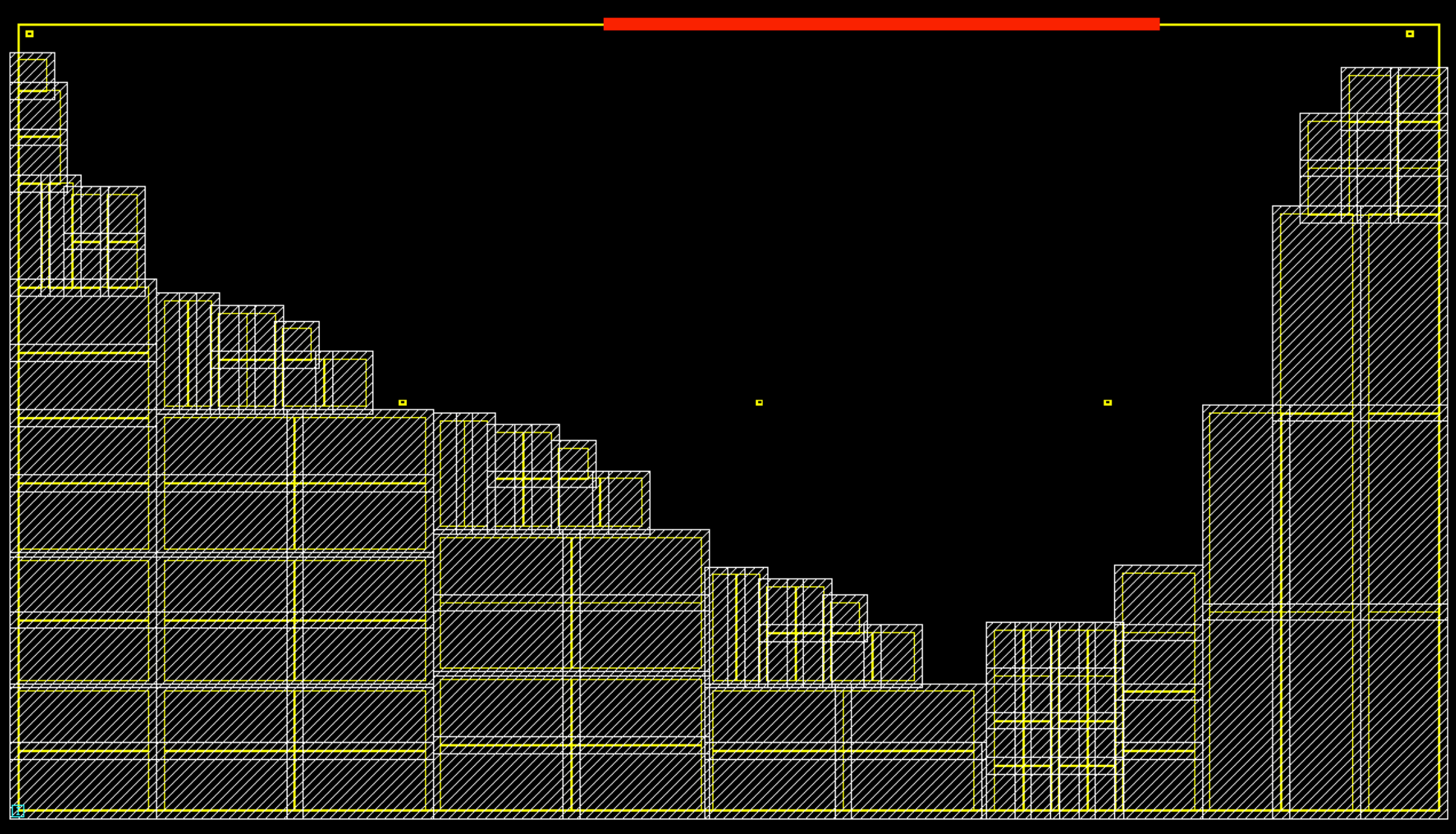

Beta본 글은 Google의 'Chip Placement with Deep Reinforcement Learning' 논문을 소개하며, 반도체 설계 공정 중 하나인 Chip Placement 문제를 딥러닝 기반 강화학습으로 해결하는 방안을 다룹니다. Chip Placement는 반도체 설계 도면(Netlist)의 소자(Macro, Standard Cell)들을 주어진 공간(Chip Canvas)에 배치하여 성능, 전력, 면적 등 최적의 결과를 얻는 조합 최적화 문제입니다.

기존의 휴리스틱 알고리즘은 복잡성과 최적화 한계가 있었으나, 강화학습은 이러한 문제를 해결할 잠재력을 보여줍니다. 논문에서는 강화학습 에이전트가 배치 결정을 내리고, 이를 통해 기존 방법론 대비 우수한 성능을 달성했음을 설명합니다.

이는 AI 기술이 복잡한 공학 문제 해결에 어떻게 기여할 수 있는지 보여주는 사례입니다.

이 글이 궁금하신가요?

원문 블로그에서 전체 내용을 확인해 보세요

원문 읽으러 가기