주문형 반도체 (ASIC) Floorplan 자동화 - Part II

강화학습ASICFloorplan반도체 설계배치 최적화머신러닝

AI 요약

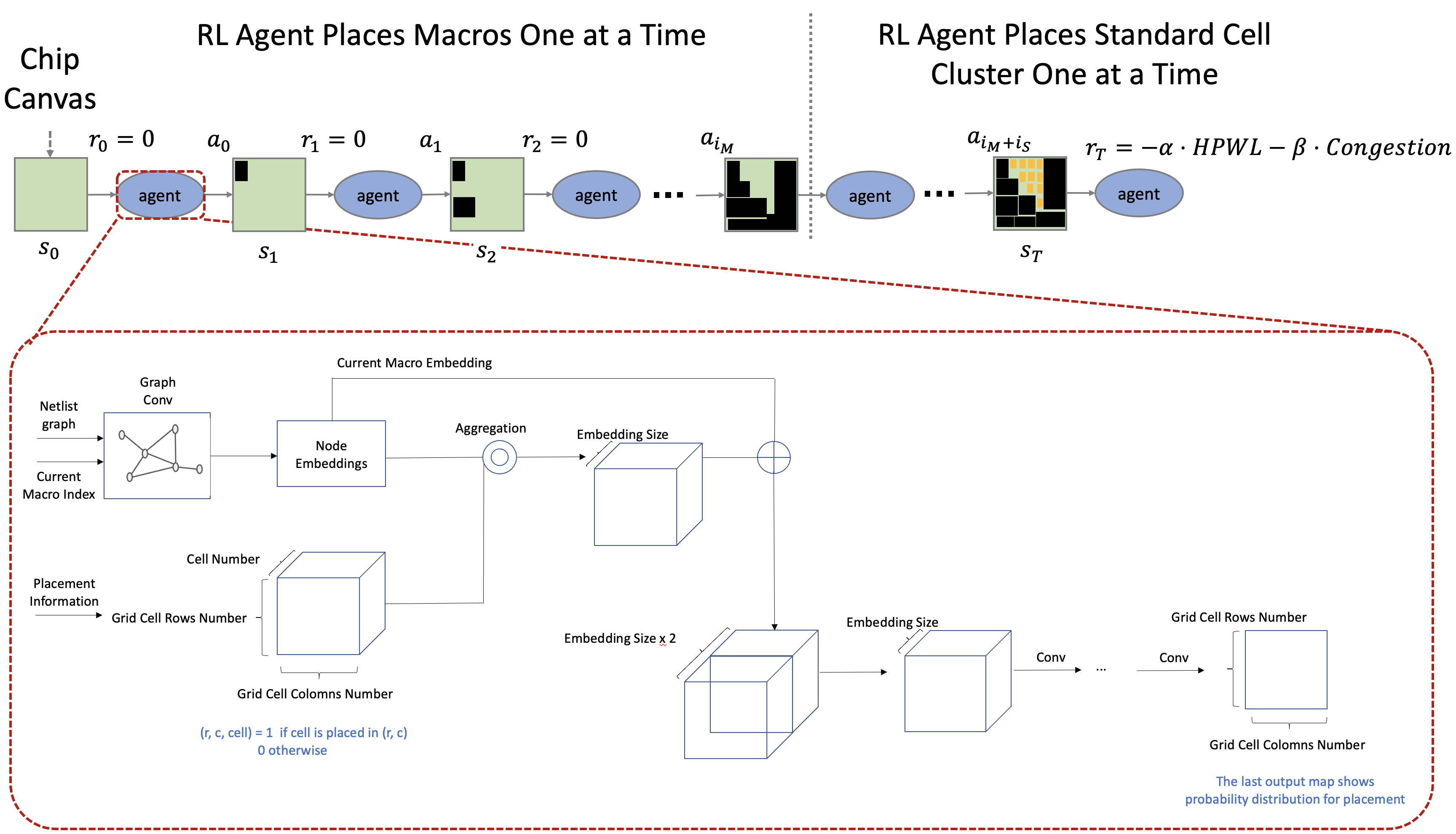

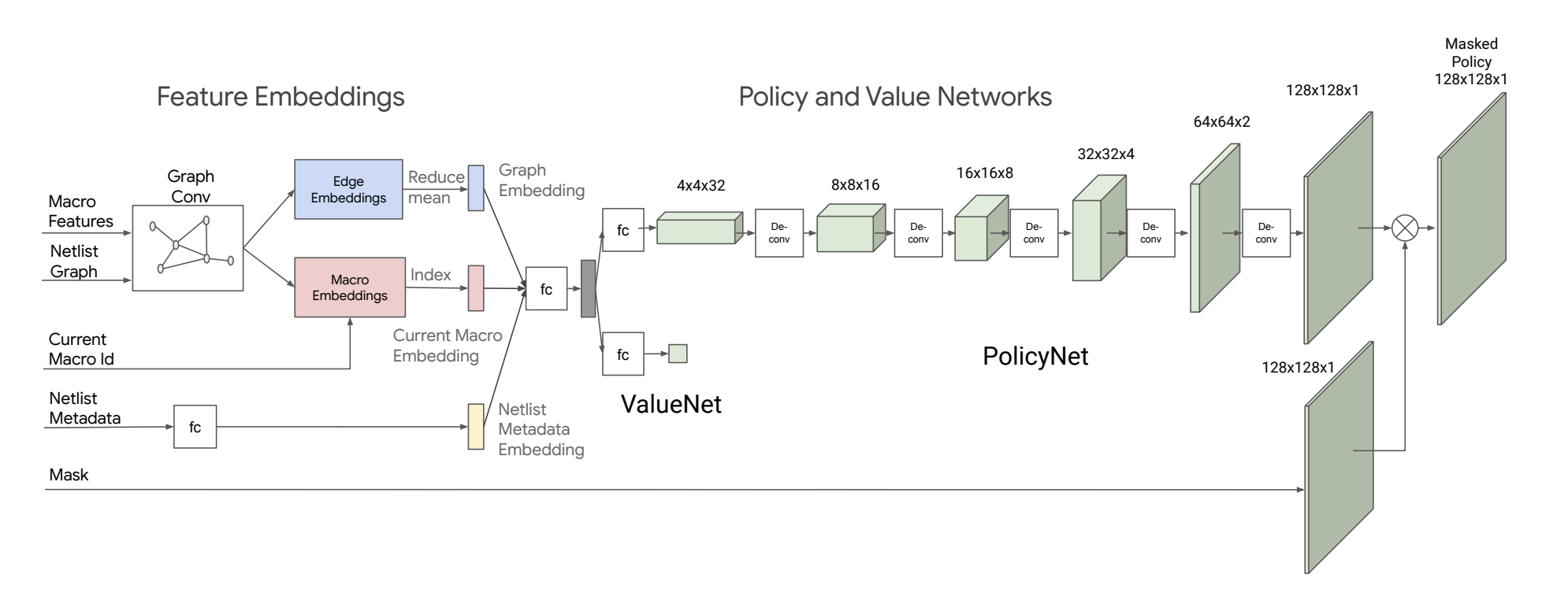

Beta본 글은 주문형 반도체(ASIC) 설계의 Floorplan 단계에서 발생하는 배치 최적화 문제를 강화학습을 이용하여 해결하는 프로젝트를 소개합니다. 특히 구글에서 발표한 'A graph placement methodology for fast chip design' 논문에 기반하여, 수십~수백만 개의 트랜지스터 연결성을 고려해야 하는 복잡한 Floorplan 과정의 자동화를 목표로 합니다.

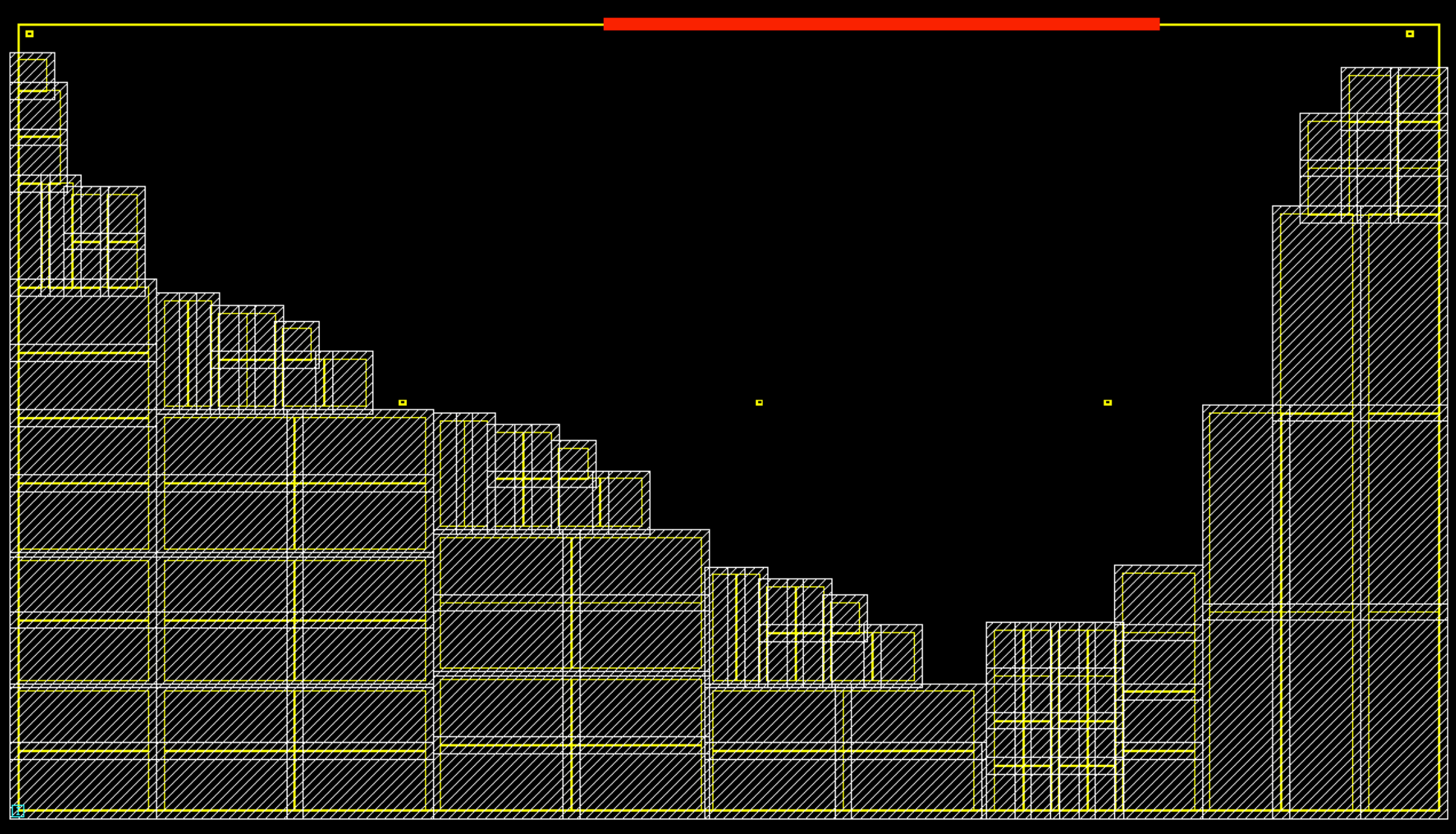

Macro와 Standard Cell이라는 주요 소자들의 배치를 최적화하는 과정을 다루며, 강화학습 에이전트가 Macro는 칩 바깥쪽에, Standard Cell Cluster는 안쪽에 배치하도록 학습하는 애니메이션을 통해 그 효과를 시각적으로 보여줍니다. 약 5개월간의 프로젝트 경험을 바탕으로 Floorplan 문제에 대한 이해부터 솔루션 구현까지의 과정을 공유하며, 산업의 난제에 도전하는 강화학습의 가능성을 제시합니다.

이 글이 궁금하신가요?

원문 블로그에서 전체 내용을 확인해 보세요

원문 읽으러 가기